AMD Zen 6 and Zen 7 will feature vertical cache under CCD

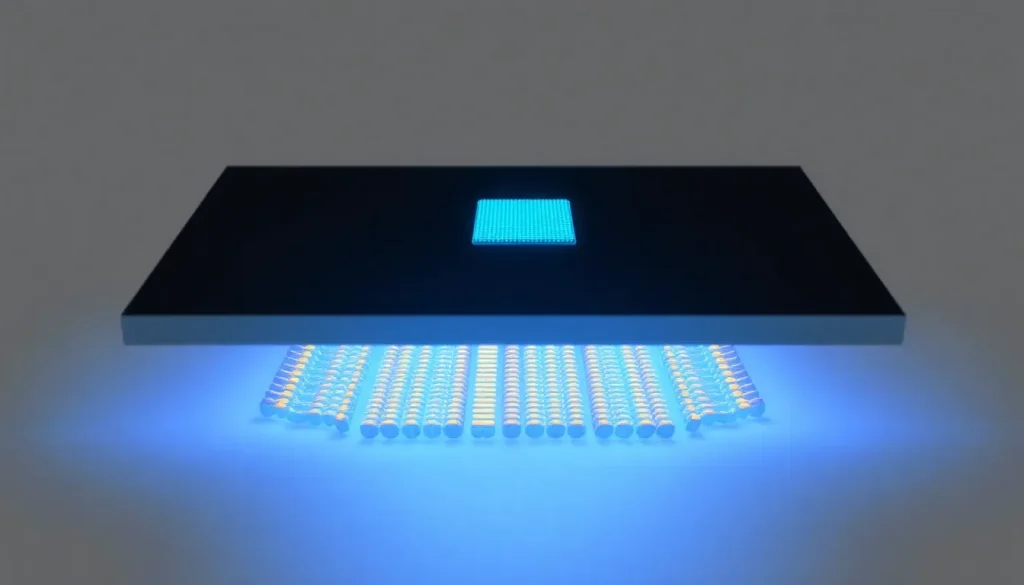

AMD continues to make strides in the realm of CPU technology, particularly with its upcoming Zen 6 and Zen 7 architectures. Recent leaks suggest that AMD will stick to its successful vertical cache strategy, employing a 3D V-Cache positioned beneath the chiplet die (CCD). This not only enhances thermal efficiency but also allows for a straightforward design, facilitating the integration of various cache types. This approach has already proven effective in AMD’s product line, notably with the Ryzen 7 9800X3D, which currently leads the market.

AMD Zen 6 and Zen 7 will utilize vertical cache beneath the CCD, similar to Zen 5

AMD is employing extremely thin silicon bridges combined with organic RDL interposers in Zen 6 and Zen 7. This method is both cost-effective and efficient compared to larger silicon interposers used by competitors like Intel. The use of Silicon Bridges (SB) and Fan-Out Embedded Bridge (FOEB) technologies facilitates a direct connection between the stacked cache and the chiplet, significantly enhancing memory bandwidth while reducing latency and overall power consumption.

This means that Zen 7 will inherit the same V-Cache technology as Zen 6, ensuring a comparable thermal performance and configuration. The expectation is that by the end of 2026, we could witness the introduction of the first Ryzen 11000 X3D models, taking advantage of these technological advancements.

Intel's Vertical Cache Strategy and AMD's Response

The confirmation that Zen 6 and Zen 7 will feature vertical cache beneath the CCD sets the stage for AMD to explore further customization options. While it’s suggested that AMD might deploy both SB and FOEB technologies across its product range, including lower-end CPUs and GPUs, a more tailored approach to vertical cache could be in the works.

If AMD moves forward with the patent outlining three types of vertical cache implementations, we could see a significant diversification based on product requirements. The three potential implementations include:

- F2B Piring Die Back: Both dies feature BPR (1700A), where energy delivery occurs from the back of the lower die (L3 cache) to the DDR5 or DDR6 via TSV, connecting to the upper die through hybrid unions.

- F2B Top Die Back: Only the lower die delivers energy (1700B), with the connection running from the back of the lower die to the upper die.

- F2B Top Die Back (1700C): Both cache die and core die have BPR on their rear sides, ensuring adequate power supply from the AID, which could be DDR6.

Specific Vertical Cache Solutions for Different Products

Looking ahead, the Ryzen 11000 X3D series could benefit from a specific vertical cache design that enhances performance tailored for high-demand applications. Additionally, variants aimed at gaming consoles, like the upcoming PS6 or Xbox Magnus, might utilize dedicated vertical cache solutions to optimize GPU performance.

The flexibility of AMD’s vertical cache technology could allow the company to determine which of the three implementations to deploy across its product lines. This adaptability could lead to a competitive edge, especially if Intel's upcoming Nova Lake architecture proves to be formidable in the gaming market.

When can we expect AMD Zen 6 to launch?

As for the timeline, the AMD Zen 6 architecture is anticipated to debut in late 2026. The company is making preparations to ensure that the transition to this new technology is seamless, aiming to integrate the vertical cache strategy effectively.

AMD's recent announcements and product roadmaps suggest that the launch of Zen 6 will coincide with significant advancements in both performance and efficiency, further solidifying its standing in the CPU market. The integration of advanced cache technologies is a clear indication of AMD’s commitment to innovation.

What is AMD's 3D V-Cache technology?

The 3D V-Cache technology is a revolutionary approach to increasing the cache memory available to processors. By stacking cache memory vertically, AMD can enhance the performance of its CPUs without significantly increasing the physical footprint of the chip. This technology allows for:

- Increased bandwidth: The vertical stacking reduces the distance data must travel, enhancing communication speed between the CPU and cache.

- Lower latency: Direct connections between the cache and processing units minimize delays, improving overall performance.

- Energy efficiency: Reduced power consumption is achieved by optimizing the design, leading to less heat generation.

This technology has been demonstrated in AMD’s high-end CPUs, providing a competitive edge over traditional cache designs.

How does AMD's Ryzen Zen 2 processor perform?

The Ryzen Zen 2 processors have set a high standard in the CPU market, offering impressive performance across various applications. With multiple cores and threads, these processors excel in multitasking and handling demanding workloads. Key features include:

- Advanced architecture: The Zen 2 architecture improves IPC (instructions per clock) performance, leading to faster processing capabilities.

- Support for PCIe 4.0: This allows for faster data transfer rates with compatible devices, such as SSDs and GPUs.

- Energy efficiency: The 7nm manufacturing process contributes to lower power consumption and heat generation.

The Ryzen Zen 2 series has proven to be a strong contender in both gaming and professional environments, making it a preferred choice for many users.

For those interested in a deeper dive into AMD's upcoming architectures, this video provides valuable insights into the future of AMD processors:

Leave a Reply